| The number of full and half adders are required to add 16-bit number is                        |

|------------------------------------------------------------------------------------------------|

|                                                                                                |

|                                                                                                |

| o a. 16 half adders, 0 full adders                                                             |

| <ul> <li>b. 4 half adders, 12 full adders</li> <li>c. 1 half adders, 15 full adders</li> </ul> |

| od. 8 half adders, 8 full adders                                                               |

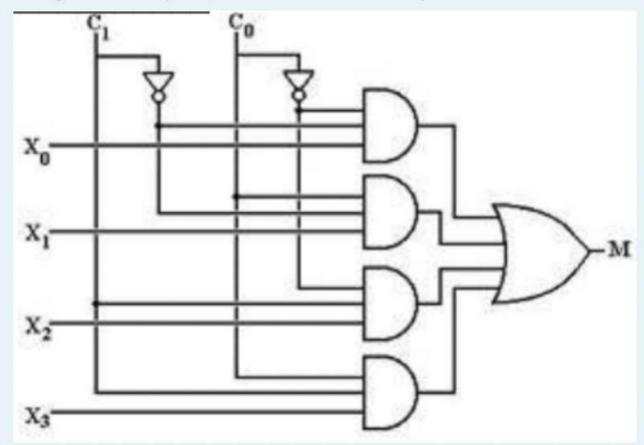

In the given 4-to-1 multiplexer, if c1 = 0 and c0 = 1 then the output M is

- a. X0 OR X3

- b. X1

- O c. X3

- od. X0

- O e. X2

The binary numbers A = 1100 and B = 1001 are applied to the inputs of a comparator. What are the output levels?  $\bigcirc$  a. A > B = 1, A < B = 0, A < B = 1b. None  $\bigcirc$  c. A > B = 1, A < B = 0, A = B = 0 $\bigcirc$  d. A > B = 0, A < B = 1, A = B = 0  $\bigcirc$  e. A > B = 0, A < B = 1, A = B = 1 If two inputs are active on a high priority encoder, which will be coded on the output? a. The higher value b. The lower value o. Both of the inputs

d. Neither of the inputs

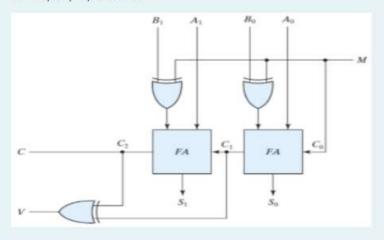

For the following two-bit adder/subtractor with overflow detection. If inputs M=0, two unsigned numbers A1A0= 01, B1B0= 01, what's the value of \$1, \$0, \$C, and \$V\$?

- a. \$1 \$0 = 10, C= 1, V= 0

- b. \$1 \$0 = 10, C=1, V=

- L = 0

- O c. \$1 \$0 = 01, C= 1, V= 0

- od. \$1 \$0 = 11, C= 1, V= 0

- e. \$1 \$0 = 10, C= 0, V= 0

The difference between the full adder and half adder is

- a. Half adder has two inputs while full adder has four inputs

- o b. Half adder has no input while full adder has three inputs

- © c. Half adder has two inputs while full adder has three inputs

- od. Half adder has one input while full adder has two inputs

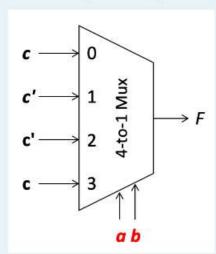

The following 4 x 1 multiplexer implements the function F that has an expression

$$\bigcirc$$

a.  $F(a, b, c) = \sum (0, 3, 5, 6)$

ⓐ b.

$$F(a, b, c) = \sum(1, 2, 4, 7)$$

$$\bigcirc$$

c.  $F(a, b, c) = \Pi(0, 1, 3, 5, 6)$

$$\bigcirc$$

d.  $F(a, b, c) = \sum (1, 2, 4, 6)$

$$\bigcirc$$

e.  $F(a, b, c) = \Pi(1, 2, 4, 7)$

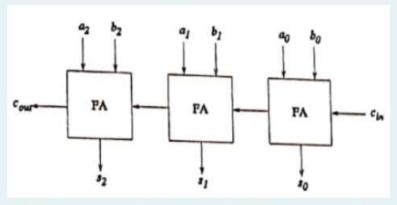

## Consider the following diagram of a 3-bit adder:

What is the value of s2, s1, s0 and Cout, if a2a1a0 = 101 and b2b1b0= 110 and Cin =0 ?

## Select one:

- a. s2 s1s0 = 011 and Cout= 1

- b. s2 s1s0 = 010 and Cout= 1

- oc. s2 s1s0 = 0110 and Cout= 1

- d. s2 s1s0 = 001 and Cout= 1

- e. s2 s1s0 = 011 and Cout= 0

The following switching functions are to be implemented using a decoder:  $f1 = \sum m(1, 2, 4, 8, 10, 14)$   $f2 = \sum m(2, 5, 9, 11)$   $f3 = \sum m(2, 4, 5, 6, 7)$  The minimum configuration of decoder will be \_\_\_\_\_\_

- a. 5 to 32 line

- b. 2 to 4 line

- oc. 3 to 8 line

- @ d. 4 to 16 line

| Half adder circuit can be produced using a two-input gate and a two-input | gate. |

|---------------------------------------------------------------------------|-------|

| oa. NOR; NAND                                                             |       |

| O b. OR; NAND                                                             |       |

| O c. None                                                                 |       |

| d. XOR; AND                                                               |       |

| O e. OR, AND                                                              |       |